# **EXPERIMENT 10**

# Latches: SR & D-Type

### **OBJECTIVES:**

- Examine S-R, gated S-R, and gated D-type latches.

- Create the designs for the S-R, gated S-R, and gated D latches in schematic mode.

- Test the designs on the target board.

### **MATERIALS:**

- Xilinx Vivado software, student or professional edition V2018.2 or higher.

- IBM or compatible computer with Pentium III or higher, 128 M-byte RAM or more, and 8 G-byte Or larger hard drive.

- BASYS 3 Board.

## **DISCUSSION:**

In this experiment, we will discuss sequential circuits. The main difference between combinational circuits and sequential circuits is that combinational circuits do not have memory elements. So the output of a combinatorial circuit depends only on the present inputs. But the output of a sequential circuit depends on the effects of prior inputs (the memory) as well as the present inputs. Latches are simple, but very important, class of memory elements.

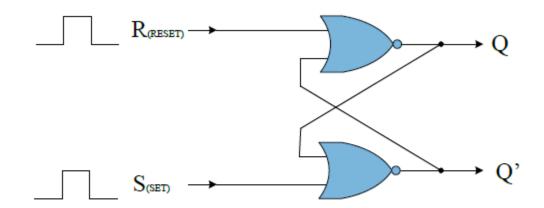

## S-R NOR Latch

The S-R NOR latch has two inputs: S and R (SET and RESET) and two outputs: Q and not Q. The Q is the normal output and not Q is the complemented output. Any latch has two states: SET and RESET (CLEAR). When Q = 1, we say the latch is in the SET state. When Q = 0, the latch is in the RESET state. Figure 11.1 shows the

Page 1 | 14

construction of a **NOR** latch. (The notation **S-C**, **SET**& **CLEAR**, is sometimes used for **SR** latches.)

Figure 11.1 SR Latch with NOR gates

The truth table below (Table 11.1) describes the characteristics of this NOR latch.

| Set (S) | Reset (R) | Q | Q' | State     | Note                      |

|---------|-----------|---|----|-----------|---------------------------|

| 1       | 0         | 1 | 0  | 1         | Set                       |

| 0       | 0         | 1 | 0  | 1         | After S=1, R=0(no change) |

| 0       | 1         | 0 | 1  | 0         | Reset                     |

| 0       | 0         | 0 | 1  | 0         | After S=0, R=1(no change) |

| 1       | 1         | 0 | 0  | Forbidden | Forbidden                 |

SR Latch (NOR) Truth Table

Table 11.1.1 The Truth Table for the SR NOR Latch

A NOR latch has active-high inputs. When both inputs are low (**S**=0, **R**=0), the output will not change. It is "latched". Normally, one of the inputs in it could be set to high to "set" or "clear" the latch. Yet if both inputs are high (**S**=1 and **R**=1), both outputs will be low, which is not valid since **Q** and **not-Q** should be opposites.

### The SR NAND Latch

| Logic Design L                | ab EEL3712I |                        |                                      |                                   | Experiment 10                              |

|-------------------------------|-------------|------------------------|--------------------------------------|-----------------------------------|--------------------------------------------|

| $S_{(SET)} \rightarrow (SET)$ |             |                        |                                      |                                   | Q → Q                                      |

|                               | ] [         | R <sub>(reset)</sub> - |                                      |                                   | Q'                                         |

|                               |             |                        | SR La                                | tch with NA1                      | ND gates                                   |

| Set (S)                       | Reset (R)   |                        | SR La                                |                                   | ND gates<br>Note                           |

| Set (S)<br>1                  | Reset (R)   | SR                     | SR La<br>Latch (NAND                 | ) Truth Table                     | _                                          |

|                               |             | SR<br>Q                | SR La<br>Latch (NAND<br>Q'           | ) Truth Table<br>State            | Note                                       |

| 1                             | 0           | SR<br>Q<br>0           | SR La<br>Latch (NAND<br>Q'<br>1      | ) Truth Table<br>State<br>0       | Note<br>Reset                              |

| 1                             | 0<br>1      | SR<br>Q<br>0<br>0      | SR La<br>Latch (NAND<br>Q'<br>1<br>1 | 0) Truth Table<br>State<br>0<br>0 | Note<br>Reset<br>After S=1, R=0(no change) |

A NAND latch has active-low inputs. When both inputs are high (S=1, R=1), the output will not change. It is "latched". Normally, one of the inputs in it could be set to high to "set" or "clear" the latch. Yet if both inputs are low (S=0 and R=0), both outputs will be low, which is not valid since **Q** and **not-Q** should be opposites.

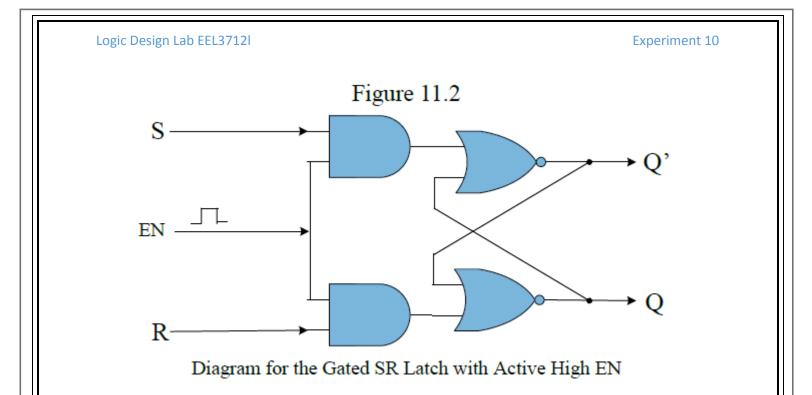

### The Gated S-R Latch

In applications, we often want to make the latch latched and ignore any inputs changes in certain period. An enable line (**EN**) is added for this purpose. As shown in Figure 11.2, two more gates are added to obtain the gated S-R latch. The gated S-R latch is also called the level-triggered **SR flip-flop** (**S-R FF**) since **Q** can change only when **EN** "pulls the trigger".

The truth table in Table 11.2 shows how the **EN** input controls when the latch can respond to the **S-R** inputs.

|    |         |           | area ore bar | ii iiadi ido |           |                  |

|----|---------|-----------|--------------|--------------|-----------|------------------|

| EN | Set (S) | Reset (R) | Q            | Q'           | State     | Note             |

| 1  | 0       | 0         | 1            | 0            | 1         | No change        |

| 1  | 0       | 1         | 0            | 1            | 0         |                  |

| 1  | 1       | 0         | 1            | 0            | 1         |                  |

| 1  | 1       | 1         | 0            | 0            | 0         | Invalid (Q=Q'=0) |

| 0  | Х       | Х         | Х            | Х            | Х         | No change        |

|    | m 11 11 |           | 0 1 0        | 1 CD T       | 4 1.4 4 1 | ' TT' 1 T'NT     |

Gated SR Latch Truth Table

Table 11.2 Truth Table for the Gated SR Latch with Active High EN

It could be found that the function of the **EN** input is to enable/disable the inputs **S** and **R**.

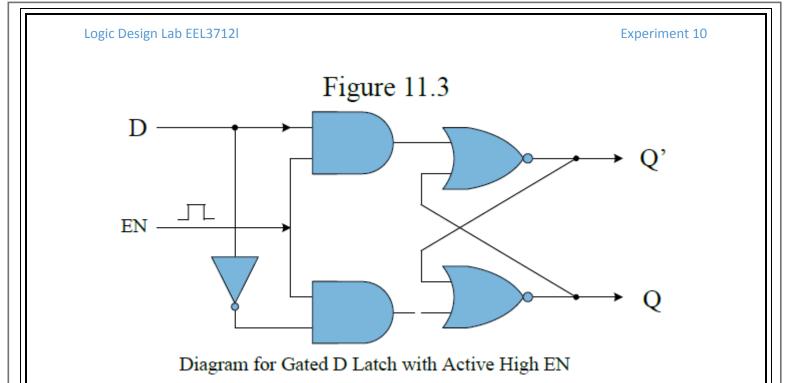

### The Gated D Latch

The gated D latch (D for data) can be built by adding an inverter before each of the two inputs in a gated S-R latch. A gated D latch is also called a level-triggered **D flip-flop (D FF)**. Its diagram is shown in Figure 11.3.

By examining the following truth table, we can see that a level-triggered **D FF** has a simple operation. The output **Q** simply follows the data input **D** when the enable input is activated. **Q** is latched when the enable is low. There is no invalid state in this latch.

| EN | D(Data) | Q | Q' | State | Note      |

|----|---------|---|----|-------|-----------|

| 1  | 0       | 0 | 1  | 0     |           |

| 1  | 1       | 1 | 0  | 1     |           |

| 0  | Х       | Х | Х  | Х     | No change |

Gated D-Latch Truth Table

Table 11.3. The Truth Table for the Gated D-Latch with Active High EN

### **PROCEDURE:** Section I. The NOR Latch and NAND Latch

1. For S-R Latches, write the following code:

```

1

library IEEE;

2 ;

use IEEE.STD LOGIC 1164.ALL;

3

4 🖯

entity S_R_latch_top is

5 ¦

Port (S: in

STD LOGIC;

R : in

6

STD LOGIC;

7

Q : inout STD LOGIC;

8

notQ : inout STD LOGIC); -- changed out to inout

9 🖂

end S_R_latch_top;

10

11 🖯

architecture Behavioral of S_R_latch_top is

12

--signal notQ : STD LOGIC;

13

begin

14

Οġ

15

<= R nor notQ;

O notQ <= S nor Q;</p>

16

17

18 🖂

end Behavioral;

```

2. Implement the simulation that is similar to the ones shown below. It is important to cover all the cases to fill your truth table.

Page 6 | 14

60 Θ

61

stim\_proc: process

#### **Experiment 10**

-- hold reset state for 100 ns.

-- insert stimulus here

begin

wait for 100 ns;

wait for 10 ns;

wait for 10 ns;

wait for 10 ns;

S <= '0';

R <= '0';

S <= '0';

R <= '1';

S <= '1';

R <= '0';

S <= '0';

wait for 10 ns;

S <= '0';

R <= '1';

wait for 10 ns;

S <= '0';

R <= '0';

S <= '1';

R <= '1';

end process;

end Behavioral;

wait for 10 ns;

wait for 10 ns;

R <= '0';

62 library IEEE; 22 63 23 use IEEE.STD\_LOGIC\_1164.ALL; 64 Ο 24 65 25 66 26 🖯 entity srSim is 0 67 27 -- Port ( ); 0 68 28 🖂 end srSim; 0 69 29 70 30 🖂 architecture Behavioral of srSim is Ο 71 31 Ο 72 32 🖯 COMPONENT S\_R\_latch\_top Ο 73 33 PORT ( 74 34 S : IN std logic; 75 Ο 35 R : IN std logic; Ο 76 36 Q : inout std logic; Ο 77 37 notQ : inout std logic 78 38 ); 79 39 🗀 END COMPONENT; Ο 80 40 Ο 41 --Inputs 81 42 signal S : std logic := '0'; Ο 82 signal R : std logic := '0'; 43 83 Ο 44 84 --Outputs 45 Ο 85 46 signal Q : std logic; Ο 86 47 signal notQ : std logic; 87 48 88 BEGIN 49 Ο 89 50 Ο 90 51 -- Instantiate the Unit Under Test (UUT) 0 91 52 🖯 uut: S\_R\_latch\_top FORT MAP ( 92 53 S => S, 93 54  $R \implies R$ , Ο 94 55  $Q \Rightarrow Q$ , Ο 95 ¦ 56 notQ => notQ Ο 96 57 🛆 ); 97 🖂 58 1 98 59 -- Stimulus process

#### 3. Next, we need to add SR-NAND Latch as following to a new file:

library IEEE; 1 2 use IEEE.STD LOGIC 1164.ALL; 3 4 🖯 entity srnand is 5 Port ( S : in STD LOGIC; R : in STD LOGIC: 6 7 Q : inout STD LOGIC; 8 notQ : inout STD LOGIC); -- changed out to inout 9 🗀 end srnand; 10 11 🖯 architecture Behavioral of srnand is 12 --signal notQ : STD\_LOGIC; 13 begin 14 O Q <= S NAND notQ;</p> 15 16 O notQ <= R NAND Q;</p> 17 18 🔶 end Behavioral;

99 🖂

100

Page 7 | 14

4. Then, the simulation program similarly:

```

22

library IEEE;

23

use IEEE.STD LOGIC 1164.ALL;

24

25 ;

26 🖯

entity srnandSim is

27

-- Port ( );

28 🖂

end srnandSim;

29 i

30 🖂

architecture Behavioral of srnandSim is

31

32 🖯

COMPONENT srnand

33

PORT (

34

S : IN std logic;

35

R : IN std logic;

36

Q : inout std logic;

37 ;

hotQ : inout std logic

38

);

39 🖂

END COMPONENT;

40

--Inputs

41

42

signal S : std logic := '0';

signal R : std_logic := '0';

43

44

45

--Outputs

signal Q : std_logic;

46

47

signal notQ : std logic;

48

49

BEGIN

50

-- Instantiate the Unit Under Test (UUT)

51 ;

52 🖯

uut: srnand PORT MAP (

S => S,

53

54

R \implies R,

55

Q => Q,

56

notQ => notQ

57 🛆

);

58

-- Stimulus process

59 i

60 🖂

stim proc: process

61

62

begin

```

5. Do not forget to change simulation settings to srNand latch simulation. Simulation results for NAND based latch should look similar to:

Page 8 | 14

| Logic Design Lab        | ) EEL3712l                     |                      |         |                                                  | Experiment 10 |

|-------------------------|--------------------------------|----------------------|---------|--------------------------------------------------|---------------|

| srnand.vh<br>Q<br>S     |                                | 8   <del>•</del>   • | H t t   | Intitled 3 × + + + + + + + + + + + + + + + + + + | Г   IHI       |

| Objects Sources Sources | Value<br>1<br>1<br>1<br>1<br>0 |                      | .333 ns | 140 ns                                           |               |

6. Fill the truth tables by using your simulation outputs.

| Set (S) | Reset (R) | Q | Q' | State | Note |

|---------|-----------|---|----|-------|------|

| 1       | 0         |   |    |       |      |

| 0       | 0         |   |    |       |      |

| 0       | 1         |   |    |       |      |

| 0       | 0         |   |    |       |      |

| 1       | 1         |   |    |       |      |

Table 11.4 Experimental Results for the SR(NOR) Latch

| SR Latch | (NAND) | Truth Table |

|----------|--------|-------------|

|----------|--------|-------------|

| Set (S) | Reset (R) | Q | Q' | State | Note |

|---------|-----------|---|----|-------|------|

| 1       | 0         |   |    |       |      |

| 1       | 1         |   |    |       |      |

| 0       | 1         |   |    |       |      |

| 1       | 1         |   |    |       |      |

| 0       | 0         |   |    |       |      |

Table 11.5 Experimental Results for the SR(NAND) Latch

Page 9 | 14

7. Compare the characteristics of the NOR latch with those of the NAND latch and comment on the differences and similarities of these two latches.

#### Section II. The Gated SR and D Latches

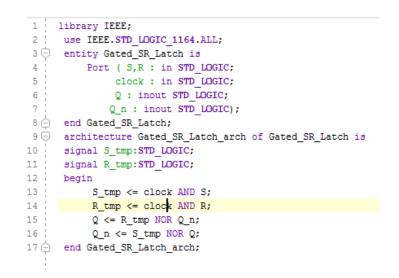

1. Write the following VHDL code for gated SR latch:

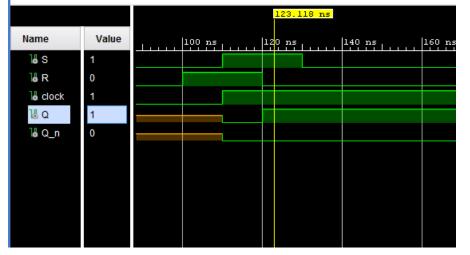

2. Implement the simulation changing variables according to your needs to fill the truth table. You should see the simulation output as shown below.

#### Experiment 10

| 22   | library IEEE;                               |

|------|---------------------------------------------|

| 23   | use IEEE.STD LOGIC 1164.ALL;                |

| 24   |                                             |

| 25   |                                             |

| 26 🖯 | entity srClocksim is                        |

| 27   | Port ( );                                   |

| 28 🗀 | end srClocksim;                             |

| 29   |                                             |

| 30 🖯 | architecture Behavioral of srClocksim is    |

| 31   |                                             |

| 32 🖯 | COMPONENT Gated_SR_Latch                    |

| 33   | PORT (                                      |

| 34   | S : IN std_logic;                           |

| 35   | R : IN std_logic;                           |

| 36   | clock : IN std_logic;                       |

| 37   | Q : inout std_logic;                        |

| 38   | Q_n : inout std_logic                       |

| 39   | );                                          |

| 40 🔶 | END COMPONENT;                              |

| 41   |                                             |

| 42   | Inputs                                      |

| 43   | <pre>signal S : std_logic := '0';</pre>     |

| 44   | <pre>signal R : std_logic := '0';</pre>     |

| 45   | <pre>signal clock : std_logic := '0';</pre> |

| 46   | 1                                           |

| 47   | Outputs                                     |

| 48   | <pre>signal Q : std_logic;</pre>            |

| 49   | <pre>signal Q_n : std_logic;</pre>          |

| 50   | 1<br>1                                      |

| 51   | BEGIN                                       |

| 52   |                                             |

|      | Instantiate the Unit Under Test (UUT)       |

| 54 📮 | uut: Gated_SR_Latch PORT MAP (              |

| 1    | S => S,                                     |

|      | $R \Rightarrow R$ ,                         |

|      | <pre>clock =&gt; clock,</pre>               |

|      | $Q \Rightarrow Q$ ,                         |

| 59   | $Q_n \Rightarrow Q_n$                       |

| 60 🖂 | );                                          |

| 61   | i                                           |

3. Fill the truth table:

Gated SR Latch Truth Table

| EN | Set (S) | Reset (R) | Q | Q' | State | Note |

|----|---------|-----------|---|----|-------|------|

| 1  | 0       | 0         |   |    |       |      |

| 1  | 0       | 1         |   |    |       |      |

| 1  | 1       | 0         |   |    |       |      |

| 1  | 1       | 1         |   |    |       |      |

| 0  | Х       | Х         |   |    |       |      |

Table 11.6 Experimental Results for the Gated SR Latch with Active High EN

4. Implement the D latch with gate by writing the following code:

Logic Design Lab EEL3712l **Experiment 10** 1 library IEEE; 2 use IEEE.STD\_LOGIC\_1164.ALL; 3 4 🖯 entity D\_Latch is GENERIC (DELAY : time := 2 ns); 5 6 Port ( Din : in STD\_LOGIC; 7 clock : in STD\_LOGIC; 8 Q : out STD LOGIC; 9 Q\_n : out STD\_LOGIC); 10 c end D\_Latch; 11 12 architecture D\_Latch\_arch of D\_Latch is 13 signal Q\_tmp:STD\_LOGIC; 14 begin 15 PROCESS (Din, clock) 16 BEGIN 17 🖯 if (clock = '1') then Q\_tmp <= Din after DELAY;</pre> 18 19 🗀 end if; 20 END PROCESS; 21 Q <= Q\_tmp; 22 Q\_n <= NOT Q\_tmp;</pre> 23 end D\_Latch\_arch;

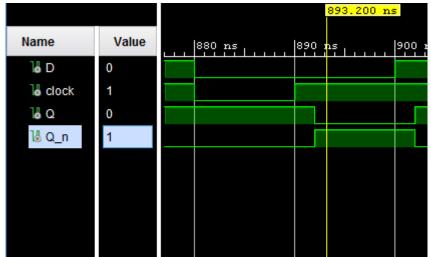

5. Prepare the simulation environment and variables. Your output should look like:

#### Logic Design Lab EEL3712

Experiment 10

| 22   | library IEEE;                           |

|------|-----------------------------------------|

| 23   | use IEEE.STD_LOGIC_1164.ALL;            |

| 24   |                                         |

| 25   |                                         |

| 26 🖯 | entity gatedDSim is                     |

| 27   | Port ();                                |

| 28 🖨 | end gatedDSim;                          |

| 29   |                                         |

| 30 🖯 | architecture Behavioral of gatedDSim is |

| 31   |                                         |

| 32 🖯 | COMPONENT D Latch                       |

| 33   | PORT (                                  |

| 34   | D : IN std logic;                       |

|      | clock : IN std logic;                   |

| 36   | Q : inout std logic;                    |

| 37   | Q n : inout std logic                   |

| 38   | );                                      |

| 39 🛆 | END COMPONENT;                          |

| 40   |                                         |

| 41   | Inputs                                  |

| 42   | signal D : std logic := '0';            |

| 43   | signal clock : std logic := '0';        |

| 44   |                                         |

| 45   | Outputs                                 |

| 46   | signal Q : std logic;                   |

| 47   | signal Q_n : std logic;                 |

| 48   |                                         |

| 49   | BEGIN                                   |

| 50   |                                         |

| 51   | Instantiate the Unit Under Test (UUT)   |

| 52 🖯 | uut: D_Latch PORT MAP (                 |

| 53   | $D \Rightarrow D$ ,                     |

| 54   | clock => clock,                         |

| 55   | $Q \Rightarrow Q$ ,                     |

| 56   | $Q_n \Rightarrow Q_n$                   |

| 57 🏳 | );                                      |

| 58   |                                         |

| 59   | Stimulus process                        |

| 60 🖯 | stim_proc: process                      |

| 61   |                                         |

| 62   | begin                                   |

|      | 1                                       |

### 6. Fill the truth table:

| Gated L | D-Latch Truth | Table |

|---------|---------------|-------|

|         |               |       |

| EN | D(Data) | Q | Q' | State | Note |

|----|---------|---|----|-------|------|

| 1  | 0       |   |    |       |      |

| 1  | 1       |   |    |       |      |

| 0  | х       |   |    |       |      |

Table 11.7 Experimental Results for the Gated-D Latch with Active High EN

Page 13 | 14

#### QUESTIONS

1) Draw the logic diagram for a gated S-R latch using only NAND gates.

2) How does the Gate or Enable inputs work in the gated latches?

3) If we want the enable input active low, what kind of modification(s) should be applied to the gated D latch? Draw the diagram.

4) How could you avoid the invalid state in an S-R latch?